VHDL PROCESSING MECHANICS

(Browser: Use Internet Explorer)

VHDL processing involve four steps:

1. Analysation

2. Elaboration

3. Initialisation

4. Execution

The basic unit of VHDL programming is a design unit. A design unit is a component of a VHDL design and could be one of:-

Entity

Architecture

Configuration

Package

Design units are contained in design files, which contain the VHDL source for individual design units. A single design file may contain the source of one or more design units.

1. Analyzation

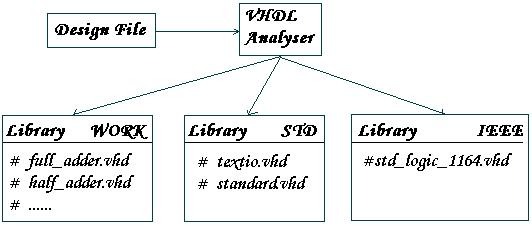

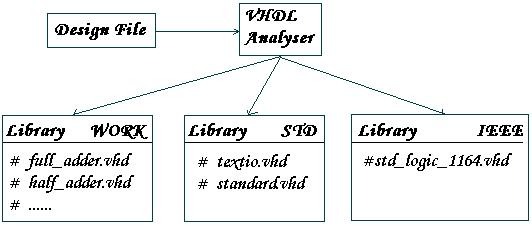

Design units are analysed to produce a form that can be used by the simulator. The VHDL Analyser performs the customary syntax checks and compilation to form executable by a VHDL simulator. The analysed design units are placed in a design library. Design libraries are typically implemented as directories in a computing environment, as shown below..

The analysed design units are placed in a design library depending on its logical source library, the default library being at the WORK library which corresponds to the working directory.If a user package is referenced in a user design unit, the package must be analysed and the compiled design unit placed in the designated library.

One important thing to note is the order of analysation VHDL programs as design units are dependent of each other. In a hierarchical structure, we must remember to analyse hierarchical descriptions in a bottom-up fashion. When we make changes to a design, we must consider dependencies between design units in determining which one must be re-analysed; it should follow the hardware analogy. Package, entity, architecture which has not changed need not be re-analysed; however packages, entities or architectures affected by design units that they contain will have to be re-analysed.

2. Elaboration

Structural models are a means of managing large designs, Before a design can be simulated it has to be flattened into a description of the system. A netlist is a common data structure that describes all of the components connected to each net. The process of flattening a hierarchical description of a design is done in the phase of elaboration. The elaboration produces a netlist of processes. Other functions are also carried out which comprises of the following:-

Elaboration of design hierarchy to flatten associating components with architecture, etc

Elaboration of declaration such as generics, signals and variables

Storage allocation for variables, signal drivers. constants & other program objects

Initialisation of all signals and variables.

3. Initialisation

Prior to execution(simulation in particular) two important actions take place. First all signals(nets) are initialised to their default or explicitly initilised values. Second, all processes are executed until they are suspended explicitly by the use of wait statements or implicitly by the use of a sensitivity list. This execution may also produce values for signals. The signal values, however, are not updated. Simulation time is set to 0 ns, and the model is ready to begin simulation. The simulator environment must maintain information about various design units involved in simulation such as location of libraries. Most simulators need access to information about the libraries (eg. IEEE, WORK, STD, etc); this is usually created and maintained in initialisation files.

4. Execution -Simulation

Simulation proceeds as a Discrete Event Simulation of the design.The synthesis part of the execution is more intricate and will not be described here.

The actual simulation of the design behaviour takes place in the execution

phase. By means of testbench processes, the VHDL model is provided with stimuli.

The individual signals of the model can then be viewed and checked in the

waveform window (stimuli and responses of the model). The actual responses can

be compared automatically with the expected values by adequate VHDL statements,

as well.

For instance you can compare actual and expected responses at time

OCCURRING_TIME by an assertion in an 'if' statement:

if now=OCCURRING_TIME then

assert EXPECTED_RESPONSE=RECEIVED_RESPONSE

report "unexpected behaviour"

severity error;

end if;